触发器是使用时钟脉冲CLK触发存储动作的单元电路。

触发器Flip-Flop需要两组或非门电路:

- 特点:一组或非门的输入是另一组的输出。

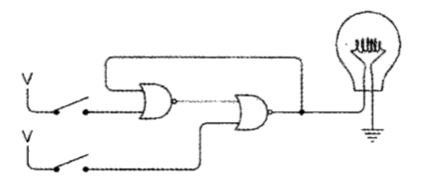

反馈:当系统的输出返回给输入,从而达到某种程度上的控制效果的时候,就说明这个系统具有了反馈的特性。- 作用:

- 当闭合上面的开关时,灯泡点亮且即使再次断开上面的开关,灯泡也不会灭。

- 这时再去闭合和断开下面的开关,灯泡就会熄灭且维持。

- 你会发现,上面的开关只能点亮灯泡,而下面的开关只能熄灭灯泡。

- 好像是灯泡会

记忆改变它状态的开关一样。

1位锁存器

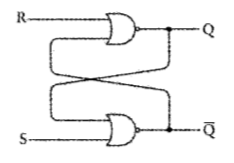

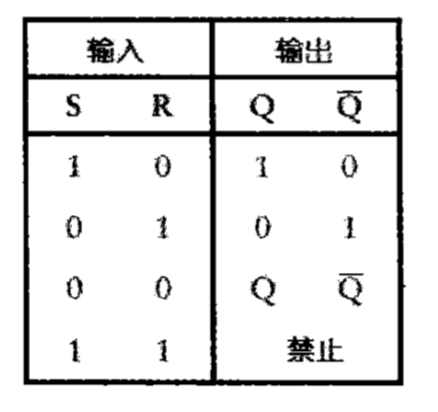

R-S触发器的设计:

R用来复位Reset,S用来置位Set,Q和Q-记录输出状态。

- 为了确保

Q和Q-互异,我们不允许R和S同时为1。

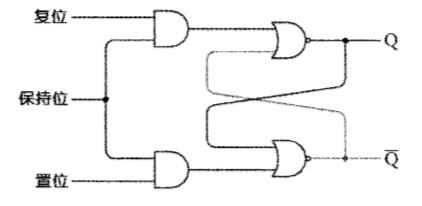

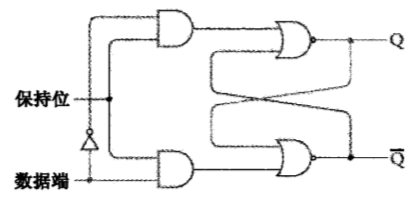

保持位的设计:

- 设置一个

保持位,保持位控制数据端的输入:保持位为0,复位和置位输入无效,保持位为1,复位和置位输入将输出到Q和Q-。 - 这就像我们键盘上的

Lock,NumLock点亮时可以输入数字,关闭时,数字键盘失效。

- 设置一个

电平触发的

D型触发器:- 将

复位和置位统一作为输入端,保持位作为控制端,设计使用电平保持位触发的数据Data输入控制器。这样的电路可以保存1位的二进制数据,所以又叫做1位存储器。

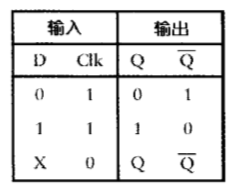

- 将

1位存储器:

- 当

Clk=0时,数据被保持,要使用这个数据,只要把输出端接到你想接到的地方就可以了,比如一个接地了的灯泡,灯泡亮与不亮就直接显示了这个锁存器存入的是0还是1。 - 如果你想改变这个锁存器存入的值,就将

Clk置为1,从输入端改变输入的值就可以了。

- 当

我的思考:

- 一开始我会觉得这种设计是多么得多余,如果你只是想要一个可以保留并输出

0和1的电路,一个继电器就可以满足需求了。 - 那为什么又要费尽周章来做这样一个复杂的触发器来做几乎完全相同的事情?

- 还记得前面我提到的一个很有趣的场景吗?

- 就像我们键盘上的

Lock,NumLock点亮时可以输入数字,关闭时,数字键盘失效。

- 就像我们键盘上的

- 我猜这么做是为了达到一种

控制,这种控制可以让你随心所欲地输入,不必受到开关只能开和关的制约。

- 一开始我会觉得这种设计是多么得多余,如果你只是想要一个可以保留并输出

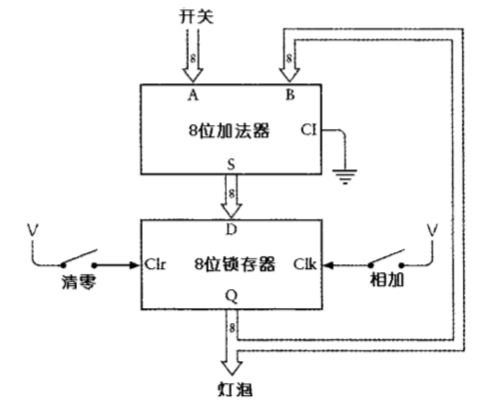

连续加法器

下图的设计原理:将加法器的结果输出给8位锁存器,然后再输出到B输入端作为加数与下一个输入的A加和,从而实现连续加和,用户只需要不断输入A的值即可。

- 首先,需要一个8位的锁存器——8个

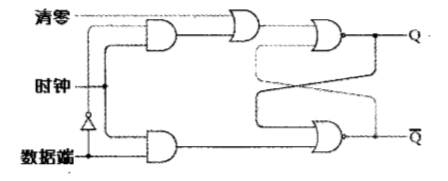

D型触发器相连,Clk串行(同一输入端)。 边沿触发器——两个

R-S触发器:要求:只有当

Clk输入从0跳到1的瞬间,数据端输入才有效

实现原理:时钟位为

0时,第二个R-S触发器处于保持位,第一个R-S触发器保存数据端输入到输出端(同时也是第二个R-S触发器的输入端),时钟位变为1的瞬间,第一个R-S触发器被保持,其输出端数据输入到第二个R-S触发器输出结果。注意:从1变为0的瞬间无效,因为两个R-S触发器的输入输出是有次序的。

清零的设计:

- 当

清零位为0时,或门输出不受影响;当清零位为1时,或门输出为1,或非门输出为0,即强制使Q端输出0。

- 当